There are several methods available to speeding up the parallel adder, one commonly used method employs the principle of look ahead-carry addition by eliminating inter stage carry logic.Ī carry-Lookahead adder is a fast parallel adder as it reduces the propagation delay by more complex hardware, hence it is costlier. Another way is to increase the circuit complexity in order to reduce the carry delay time.But there will be a capability limit for every physical logic gate. By employing faster gates with reduced delays, we can reduce the propagation delay.The following are the methods to get the high speed in the parallel adder to produce the binary addition. However, signals must be propagated through the gates at a given enough time to produce the correct or desired output.

So the speed at which the number of bits added in the parallel adder depends on the carry propagation time. If we extend the number of stages for adding more number of bits then this situation becomes much worse.

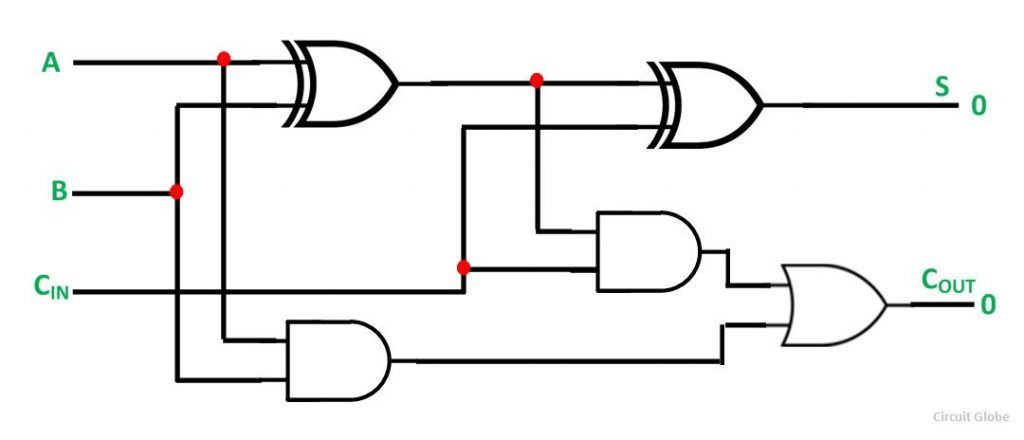

For example, if each full adder stage has a propagation delay of 20n seconds, then S4 will reach its final correct value after 80n (20 × 4) seconds. The propagation time is equal to the propagation delay of the typical gate times the number of gate levels in the circuit. Therefore, carry must propagate to all the stages in order that output S4 and carry C5 settle their final steady-state value. But the carry input C4 is not available on its final steady state value until carry c3 is available at its steady state value. In any combinational circuit, signal must propagate through the gates before the correct output sum is available in the output terminals.Ĭonsider the above figure, in which the sum S4 is produced by the corresponding full adder as soon as the input signals are applied to it. So there will be a considerable time delay in the addition process, which is known as, carry propagation delay.

In such adder circuits, it is not possible to produce the sum and carry outputs of any stage until the input carry occurs. In a parallel adder circuit, the carry output of each full adder stage is connected to the carry input of the next higher-order stage, hence it is also called as ripple carry type adder. In case of parallel adders, the binary addition of two numbers is initiated when all the bits of the augend and the addend must be available at the same time to perform the computation.

0 kommentar(er)

0 kommentar(er)